The project is divided into two phases, During Phase I, which is now complete, detailed development plans have been finalized, the RPDA package design, has been completed, FPGA functional configurations have been developed, and the overall test plan and procedures have been outlined and documented. The RPDA design objectives specification has been delivered. This document identifies high-level requirements, targeted applications information, physical design, and preliminary specifications. It covers those aspects of the RPDA that define form, fit and function (such as sub-components, physical dimensions, electrical interfaces, operating conditions, and functional capabilities). This document addresses the RPDA requirements for an un-configured device as well as the requirements for a specific functional configuration.

This project began in October 2006. A Research Management Plan and Technology Status Assessment have been completed. Additionally, the RPDA design objectives specification and a preliminary package design covering dimensions, internal component specification and placement, package materials, and connectivity, have been completed. The design provides for a high-level of test coverage for the internal components. The completed design contains a static random access memory (SRAM), a field-programmable gate array (FPGA), a non-volatile memory (high-temperature electrically erasable programmable read-only memory), and capacitors associated with the use of these high-temperature integrated circuits. FPGA simulation databases have been developed, and trial FPGA configurations have been simulated.

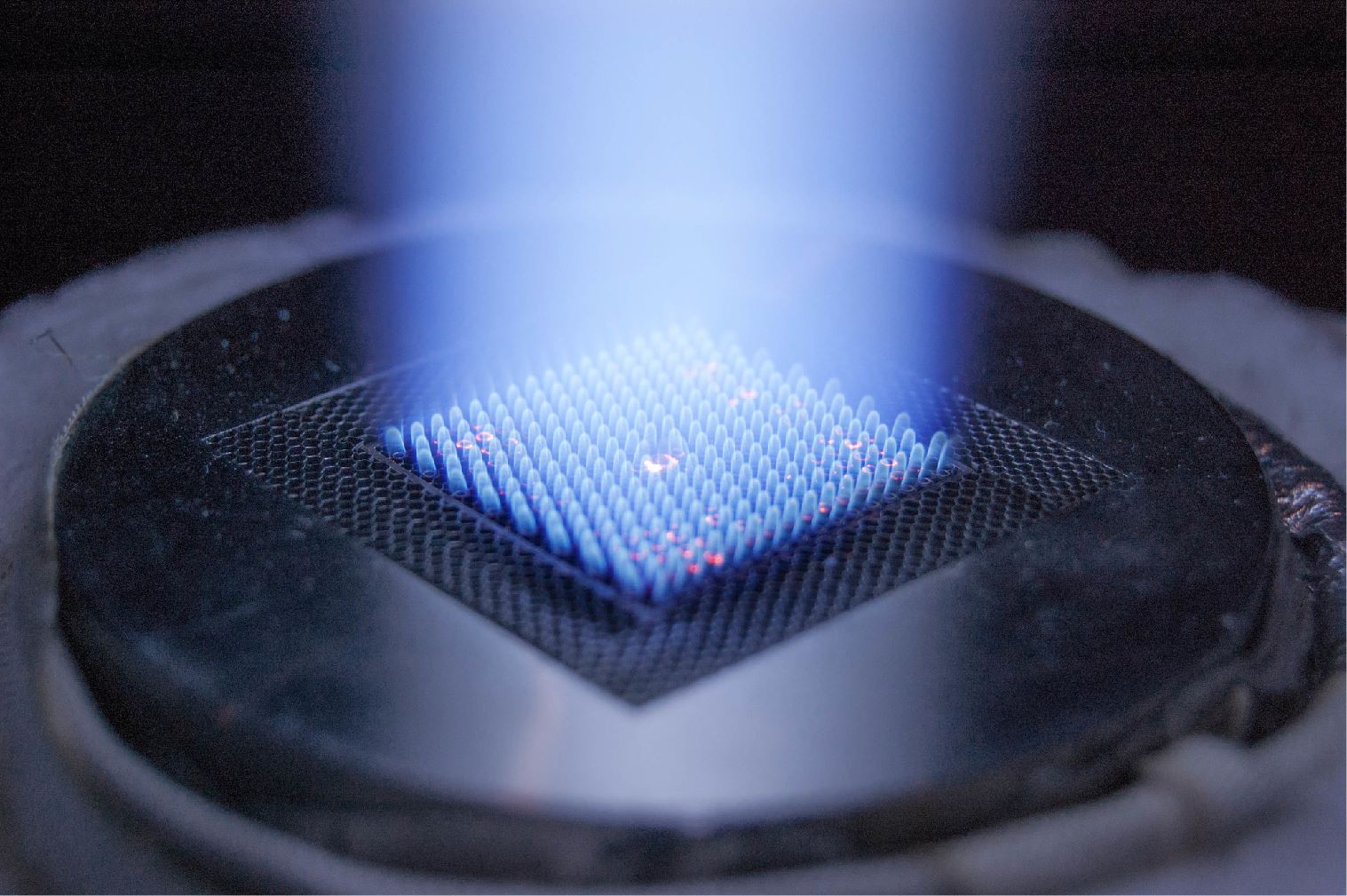

During Phase II, prototype RPDA units will be fabricated, configured, and tested, including complete characterization of configured functionality at high-temperature (225oC minimum).