# Electrodeposition of SOFC Interconnect Coatings

<sup>1</sup>H. McCrabb, <sup>1</sup>T.D. Hall, <sup>1</sup>J. Kell, <sup>1</sup>S. Snyder, <sup>2</sup>H. Zhang, <sup>2</sup>X. Liu, <sup>1</sup>E.J.Taylor

<sup>1</sup>Faraday Technology, Inc. 315 Huls Dr., Clayton, OH 45315 <sup>2</sup>West Virginia University, Dept. of Mechanical Aerospace Eng. ESB, Morgantown, WV 26506

> 12<sup>th</sup> Annual SECA Workshop July 26 – 28, 2011

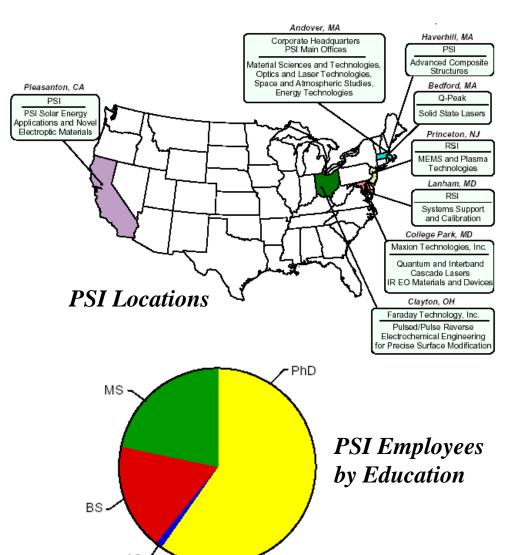

#### Faraday Technology, Inc.

- Faraday Technology specializes in electrochemical engineering

- www.faradaytechnology.com

- Faraday is a wholly-owned subsidiary of Physical Sciences, Inc. (Boston, MA)

- www.psicorp.com

- Collectively, the company staffs ~185 employees ~100 with PhDs

- Annual revenue of ~ \$50M

J-4536

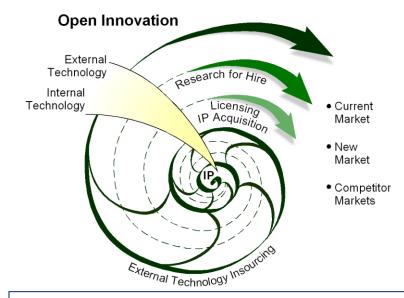

### Faraday Embraces Open Innovation

- Faraday's R&D efforts augment client company R&D needs

- Open innovation leverages government R&D dollars to solve current industrial issues.

- Faraday's strong IP portfolio reinforces our open innovation position and provides a competitive advantage for strategic partners.

26 Issued Electrochemical Patents

25 Pending Electrochemical Patents

Investment Discovery Research Knowledge Innovation Dollars

Market Dollars

### Faraday Technology, Inc.

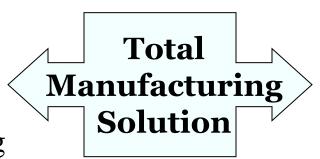

Platform

Technology:

Pulse/Pulse

Reverse Processing

**Core Competency**:

Design and Engineer of Novel Electrochemical Hardware

Either may be applied independently to improve current industrial practices or may be combined for a total manufacturing solution

- Electronics

- Edge and Surface Finishing

- Engineered Coatings

- Battery and Fuel Cell Power

- Environmental Systems

- Corrosion and Monitoring Services

- Enables uniform processing

- Applicable for additive or subtractive electrochemical processes

- Uniform processing is achieved over entire substrate, improving end product reliability

#### Objective of Program

- Develop, optimize & validate an inexpensive manufacturing process for coating metallic SOFC interconnects with Co and Mn

- Demonstrate the process's flexibility to 4"x4" and 10" x 10" single and dual-sided patterned interconnect substrates

- Control coatings nanostructure and composition to prevent

T441 exposure to O<sub>2</sub> and Cr diffusion to coating surface

- Mitigate Cr diffusion by identifying diffusion mechanism via in-situ high temperature XRD and ex-situ XPS depth profiling

- Develop a comprehensive economic assessment

- Work closely with our the SOFC industry to enhance the commercialization plan for the program.

#### Program Summary

- FARADAYIC Process allows for non-line-of-sight deposition of a wide range of compositions and surface structures using a single plating bath

- Coatings prepared using the FARADAYIC Process have uniform surface composition and thickness on 2" x 2" flat panels

- Coatings exhibit adequate adhesion

- Initial ASR and crystallinity analysis showed that the as-deposited thickness/composition had little effect on performance after a 500 hr heat cycle

- 3µm thickness is capable of minimizing Cr diffusion for 500 hr testing

- Capability to coat dual-sided 1" buttons, 4" x 4", and up to 11" x 14" panels

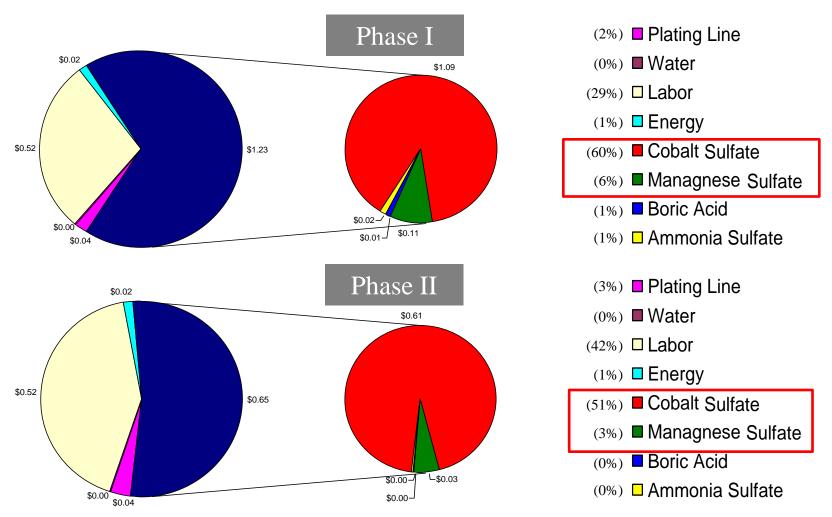

- Based on batch manufacturing, the DOE's high volume target of 1,600,000 plates per annum at a cost of ~\$1.23 per 25 x 25 cm interconnect

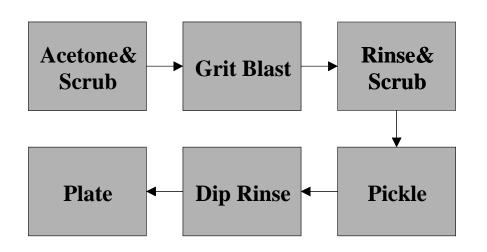

#### Coating Process

- Surface pretreatment to remove oxide and enhance coating adhesion

- Electrodeposition to coat interconnects with Mn-Co alloy

- Pulse and pulse reverse electric fields to control deposit properties

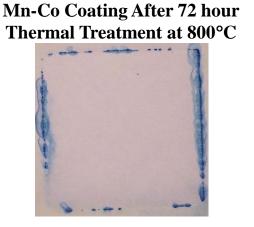

- Elevated thermal treatment to convert alloy to spinel

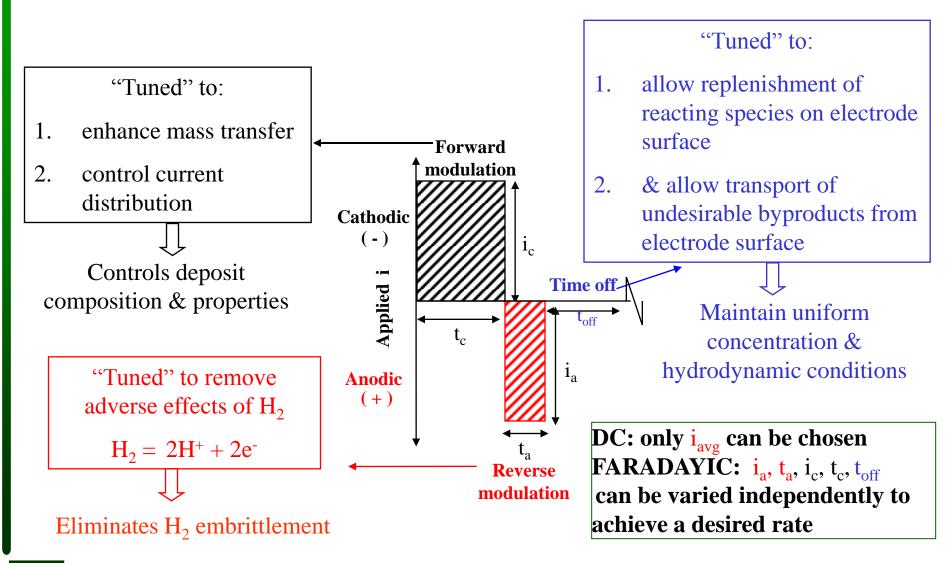

## FARADAYIC Processing

#### Initial Coating Development

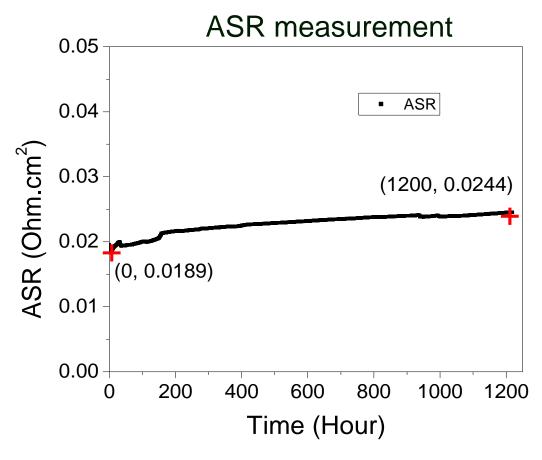

ASR prediction (40,000h, 0.0460 Ohm cm<sup>2</sup>)

J. Wu, et al., Electrochimica Acta 54 (2008) 793-800

#### Initial Coating Development

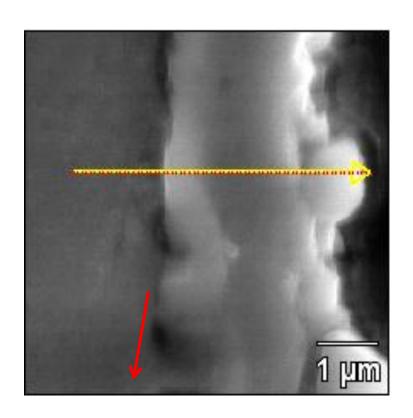

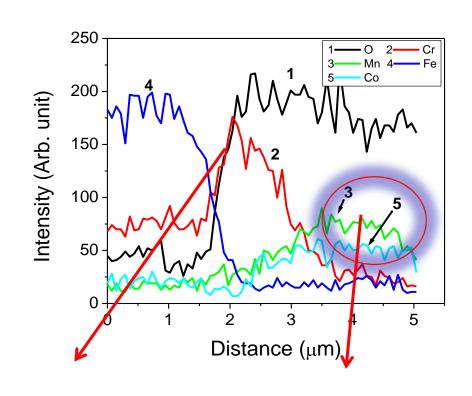

#### Cross section after ASR

Good adhesion with substrate

No Cr penetrate through the coatings

Significant Mn diffusion from substrate

### Initial Coating Development

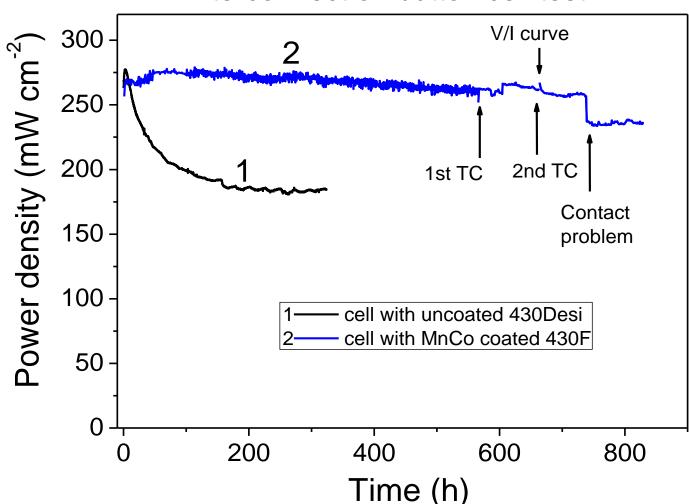

Interconnect on button cell test

With electrodeposited MnCo coating, cell performance degradation reduced

#### Objective of Phase I

- Demonstrate the technical and economic feasibility of MnCo electrodeposited on SOFC interconnect materials by answering the following questions:

- 1. What range of coating percent compositions can the electrodeposition process deposit?

- 2. Can the electrodeposition process deposit Mn-Co alloy coatings with a thickness range of 3 10 um?

- 3. How well does the coating perform at varying alloy compositions and coating thickness?

- 4. Is the electrodeposition process economically viable?

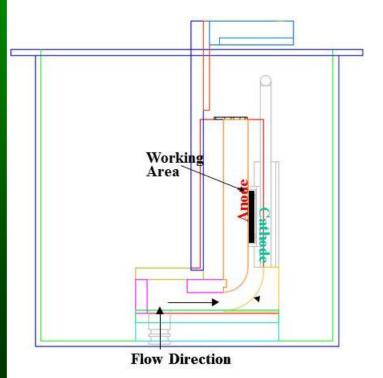

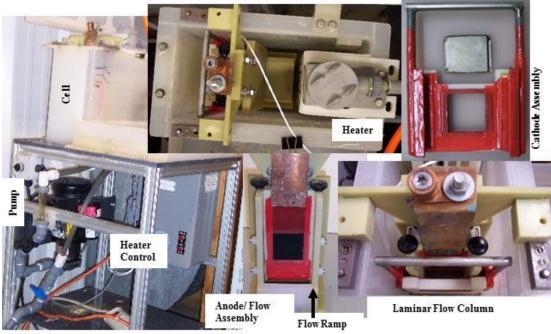

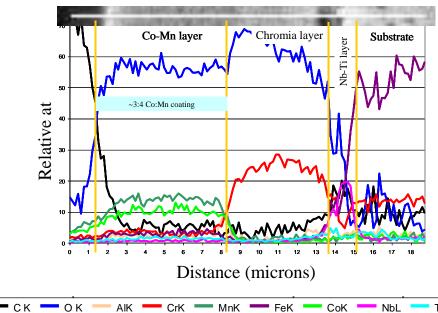

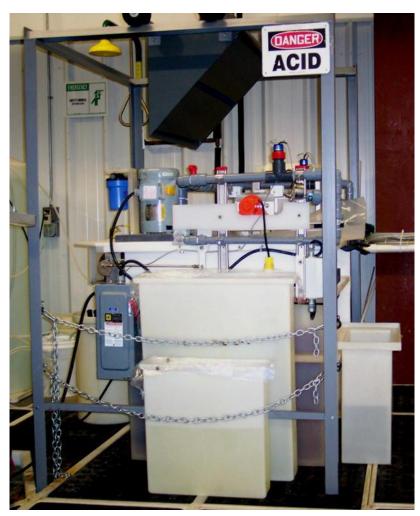

# Laboratory Scale Electrodeposition Equipment

Flow cell for plating onto 2"x2" planar T441 substrates

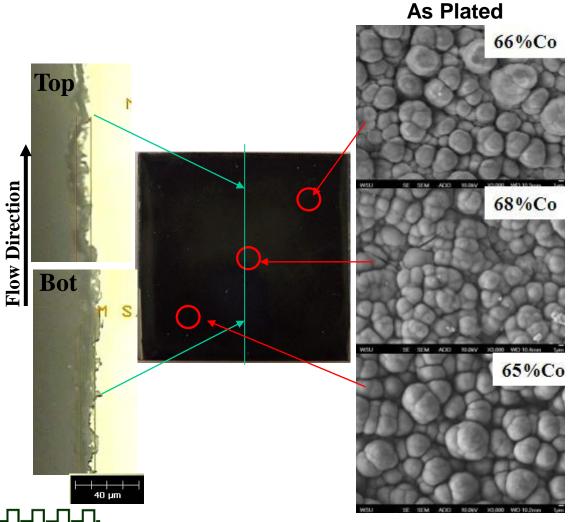

### Coating Uniformity

The electrodeposited coating exhibits a virtually uniform coating composition and thickness across the 2"x2" surface

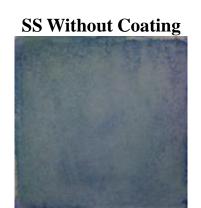

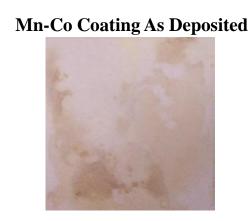

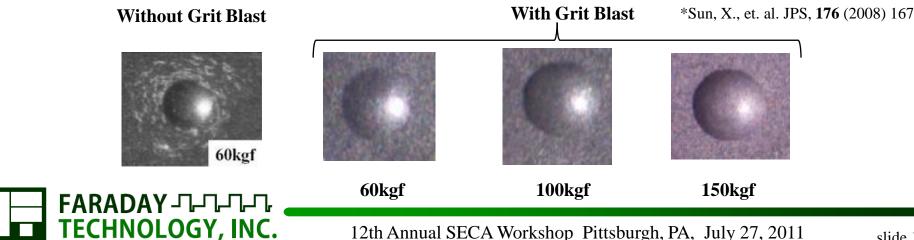

#### Coating Porosity and Adhesion

Feroxyl Porosity Test Results (AMS 2460 3.4.4.2)

\*Rockwell test with 1/16" steel ball used to quantify adhesion after spinel growth after 72 hr. at 800°C

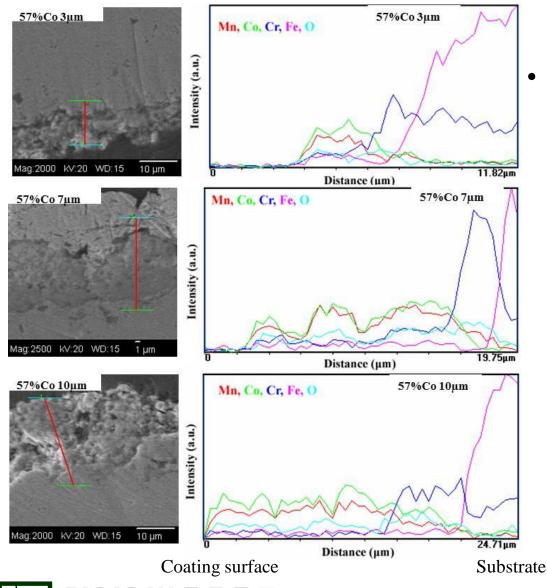

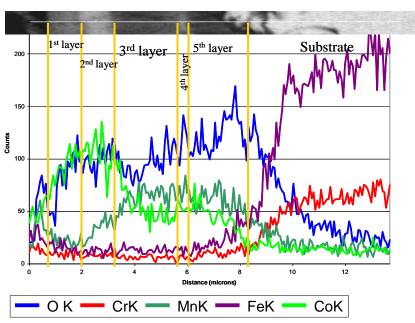

## Cr Ion Diffusion and Coating Porosity

- Cross-sections of samples that underwent a soak treatment at 800 C for 500 hrs

- Coating thickness was as deposited

- Indicates that a 3 micron layer is adequate to produce Cr complexing and minimize Cr diffusion due to minimal porosity

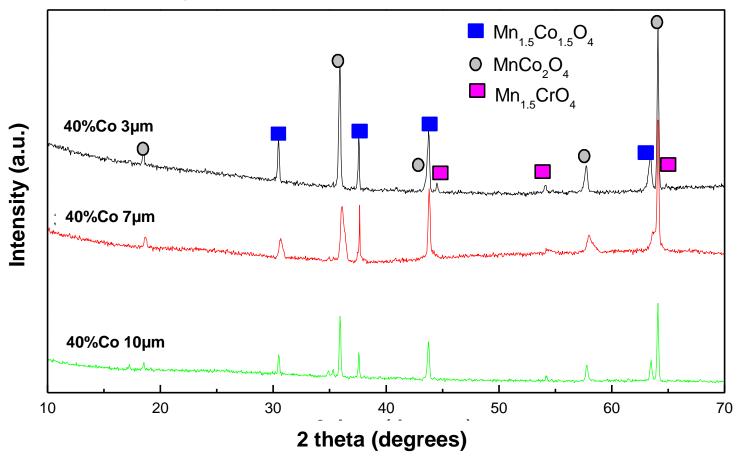

### Coating Crystal Structure

#### Crystal Structure after 500 hrs at 800°C

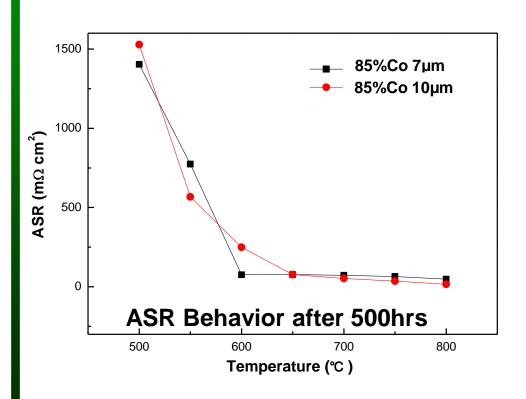

# Effect of Thickness and Composition on Performance

The ASR is  $\leq 75 \text{ m}\Omega$  cm<sup>2</sup> regardless of compositions and thickness after 500 hrs at 800 C

#### ASR at 800 C

| $m\Omega \text{ cm}^2$ | 100 hr | 200 hr | 500 hr |

|------------------------|--------|--------|--------|

| 3 μm 40% Co            | 35     | 57     | 49     |

| 7 μm 40% Co            | 62     | 7      | 32     |

| 10 μm 40% Co           | 22     | -      | 36     |

| 3 μm 85% Co            | 31     | 75     | 20     |

| 7 μm 85% Co            | 59     | 40     | 54     |

| 10 μm 85% Co           | 37     | 23     | 22     |

| 3 μm 57% Co            | -      | 34     | 26     |

| 7 μm 57% Co            | -      | -      | 12     |

| 10 μm 57% Co           | -      | -      | 12     |

#### Phase II Program Milestones

| Milestones     |                                                              |                       |                     |  |  |  |

|----------------|--------------------------------------------------------------|-----------------------|---------------------|--|--|--|

| Fiscal<br>Year | Title                                                        | Planned<br>Completion | Percent<br>Complete |  |  |  |

| 2011           | 1. Design/modification of 10" x 10" electrodeposition cell   | May 2011              | 100%                |  |  |  |

| 2011           | 2. Long-term high temperature, thermal evaluation            | September 2011        | 33%                 |  |  |  |

| 2011           | 3. Process development for 4"x4" planar interconnects        | September 2011        | 15%                 |  |  |  |

| 2012           | 4. Process development for 4"x4" pattern interconnects       | June 2012             | 0%                  |  |  |  |

| 2012           | 5. Long-term on-cell performance evaluation                  | August 2012           | 0%                  |  |  |  |

| 2012           | 6. Qualification/demonstration of IC in single cell test rig | September 2012        | 0%                  |  |  |  |

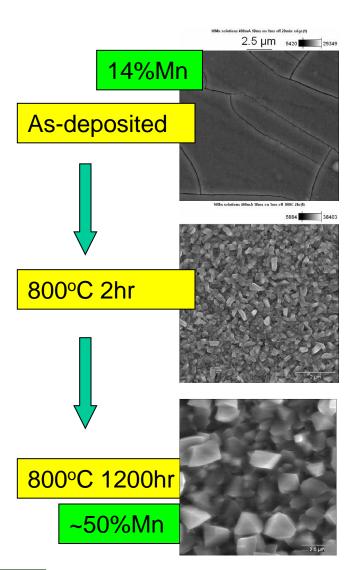

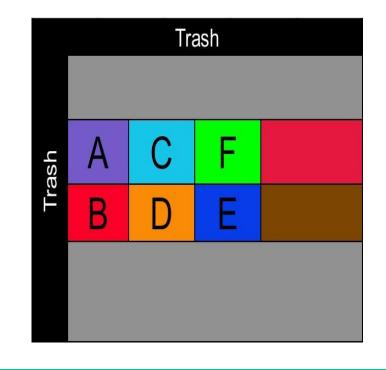

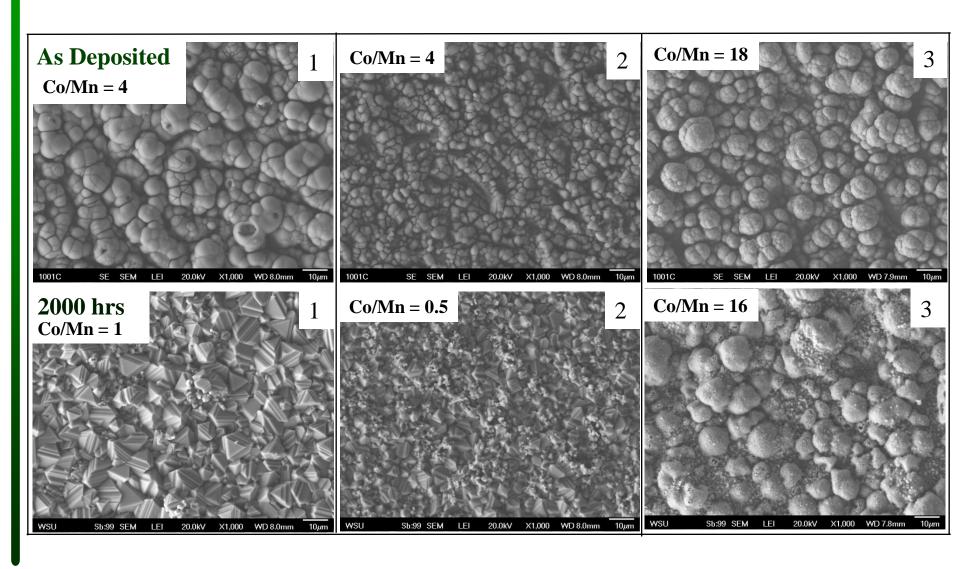

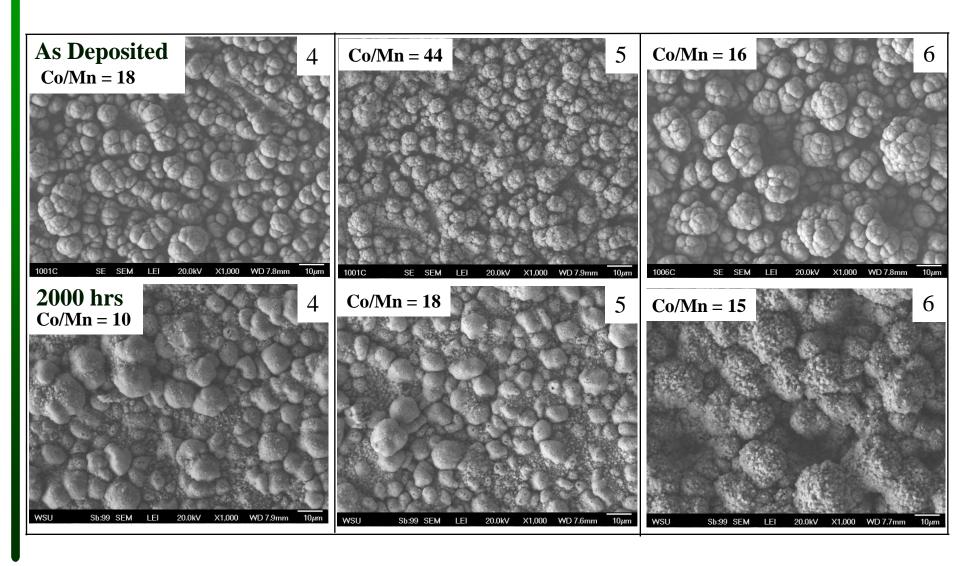

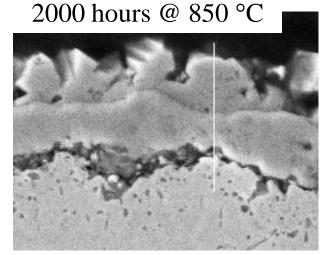

#### Extended Thermal Treatment Time Study

- Six samples were prepared using varying deposition parameters and placed into a tube furnace at 850 C.

- 2 samples with higher Mn content

and 4 with high Co content

- Target alloy thickness of 5 um

- An air flow of at least 500 sccm flows through the furnace tube (to simulate air in SOFC systems)

- Samples examined after 750, 1500, and 2000 hr

ASR Test order:C(t=0); D(t=750 hrs); E(t=1500 hrs); F(t=2000 hrs); and A(t=2000 hrs) (for Rockwell Test)

#### Extended Thermal Treatment Time Study

#### Extended Thermal Treatment Time Study

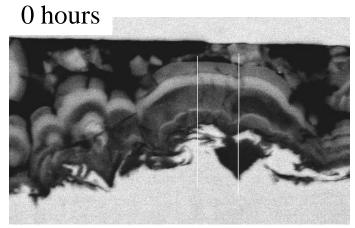

#### Cross Section Results - 1001

#### Pilot Scale Electrodeposition Equipment

Based upon Faraday's electrochemical cell design that facilitates uniform flow across the surface of a flat substrate (US patent #7,553,401)

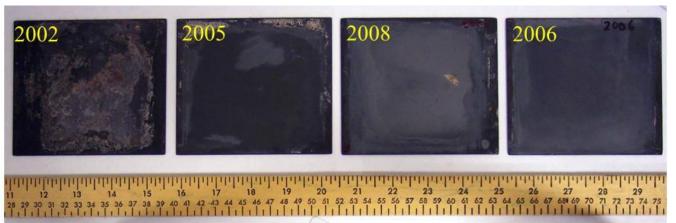

#### Initial Pilot Scale Experiments

FARADAYIC Electrodeposition parameters varied for experiments conducted in the newly modified FARADAYIC Electrodeposition Cell

| mounted Title Dieter out position cen |                          |                         |           |             |  |  |

|---------------------------------------|--------------------------|-------------------------|-----------|-------------|--|--|

|                                       | <b>Electrode Spacing</b> | <b>Electrolyte Flow</b> |           |             |  |  |

| Trial No                              | (inches)                 | (PSI)                   | Vibration | Oscillation |  |  |

| 2001                                  | 3                        | 16                      | -         | -           |  |  |

| 2002                                  | 1.5                      | 16                      | -         | -           |  |  |

| 2003                                  | 4.5                      | 16                      | -         | -           |  |  |

| 2004                                  | 4.5                      | 10                      | 50        | 50          |  |  |

| 2005                                  | 4.5                      | 16                      | 50        | 50          |  |  |

| 2006                                  | 3                        | 16                      | 50        | 50          |  |  |

| 2008                                  | 3                        | 5                       | 50        | 50          |  |  |

| 2009                                  | 3                        | 10                      | 50        | 50          |  |  |

#### Electrodeposition Cost Analysis

High volume manufacturing of 1,600,000 plates per annum at a cost of ~\$1.23 per 25 x 25 cm interconnect

#### Future Direction

- Determine plating parameters effect on chromium and oxygen diffusion

- Continue scale-up development for large area planar T441 substrates

- Begin scale-up development for large area pattern interconnects

- Demonstrate coating uniformity and composition

- Testing in single cell and short stack SOFC systems

#### Acknowledgments

- Briggs White and the entire SECA program management team

- This material is based upon work supported by the Department of Energy under Award Nos. DE-SC0001023 and DE-FE0006165. Any opinions, findings, conclusions and recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the DOE.

- Contact Information:

Heather McCrabb

Ph: 937-836-7749

Email: heathermccrabb@faradaytechnology.com

Thank You!